## 555

## Incredible Chip

delabs.net

#### TIMER

555

#### LINEAR INTEGRATED CIRCUITS

#### DESCRIPTION

The NE/SE 555 monolithic timing sincult is a highly stable controller capable of producing accurate time delays, or oscillation. Additional terminals are provided for triggering or resetting if desired, in the time delay mode of operation, the time is précisely controlled by one external resistor and dispacitor. For a stable operation at an atcillation, the free running frequency and the duty cycle are both accurately controlled with two external resistors and one capacitor. The circuit may be triggered and reset on falling waveforms, and the output structure can source or sink up to 200mA or drive TTL circuits.

#### **FEATURES**

- . TIMING THROUGH NINE DECADES

- OPERATES IN BOTH ASTABLE AND MONIOSTABLE MODES

- ADJUSTABLE DUTY CYCLE

- HIGH CURRENT OUTPUT CAN SOURCE OR SINK 200mÅ

- . OUTPUT CAN DRIVE TTL

- TEMPERATURE STABILITY OF 0.05% PER °C

- . NORMALLY ON AND NORMALLY OFF DUTPUT

#### APPLICATIONS

PRECISION TIMING

PULSE GENERATION

SEQUENTIAL TIMING

TIME DELAY GENERATION

PULSE WIDTH MODULATION

PULSE POSITION MODULATION

MISSING PULSE DETECTOR

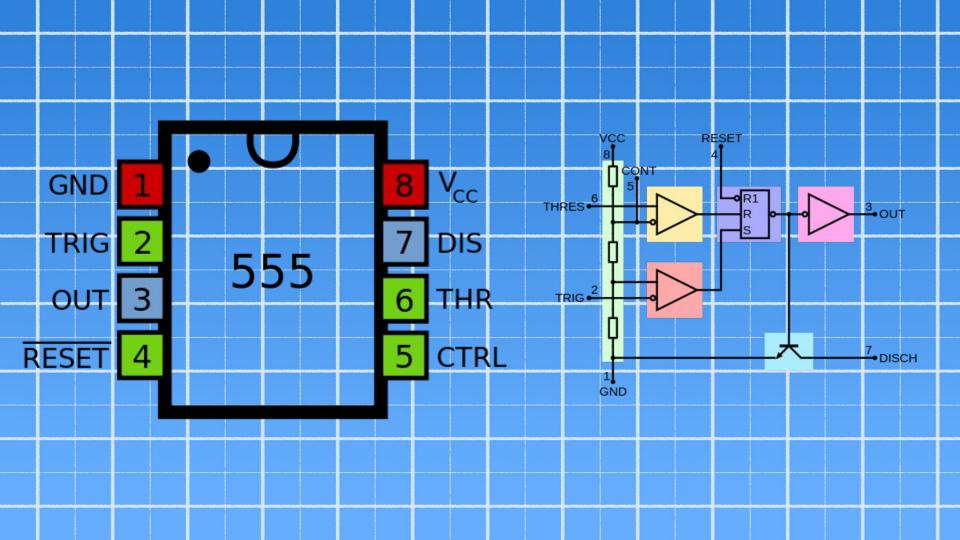

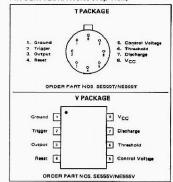

#### PIN CONFIGURATIONS (Top View)

#### ABSOLUTE MAXIMUM RATINGS

Supply Voltage

+18V

Power Dissipation

500 mW

Operating Temperature Range

0°C xe +70°C

NEB55

0°C xe +70°C

SEB55

−55°C to +126°C

Storage Temperature Range

−65°C to +150°C

Lead Temperature (Soldering, 60 seconds)

+300°C

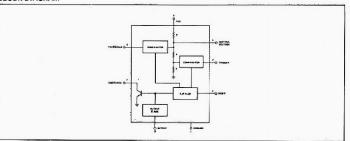

#### **BLOCK DIAGRAM**

#### SIGNETICS TIMER = 555

#### ELECTRICAL CHARACTERISTICS T<sub>A</sub> = 25°C, V<sub>CC</sub> = +5V to +15 unless otherwise specified

| PARAMETER                  | TEST CONDITIONS                          |      | SE 555 |            |       | NE 555   |      |        |

|----------------------------|------------------------------------------|------|--------|------------|-------|----------|------|--------|

|                            |                                          | MIN  | TYP    | MAX        | MIN   | TYP      | MAX  | UNITS  |

| Supply Voltage             |                                          | 4.5  |        | 18         | 4.5   |          | 16   | v      |

| Supply Current             | VCC = 5V RL = ∞                          |      | 3      | 5          |       | 3        | 6    | mA     |

|                            | V <sub>CC</sub> = 15V R <sub>L</sub> = ∞ |      | 10     | 12         |       | 10       | 15   | mA     |

|                            | Low State, Note 1                        |      |        |            |       |          |      |        |

| Timing Error               | R <sub>A</sub> , = 1KΩ to 100KΩ          |      |        |            |       |          |      |        |

| Initial Accuracy           | C = 0.1 µF Note 2                        |      | 0.5    | 2          |       | 1        |      | %      |

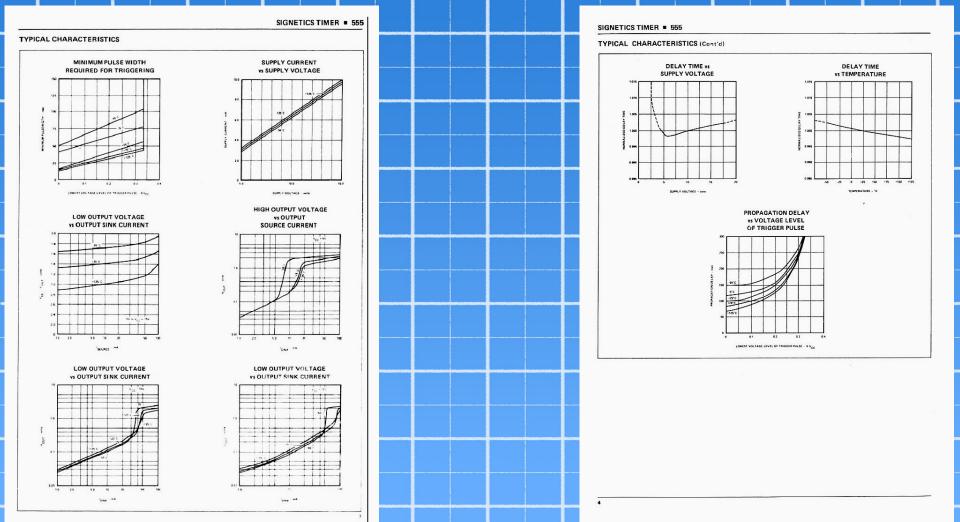

| Drift with Temperature     | see Fig. 1a VCC = 15V                    |      | 30     | 100        |       | 50       |      | ppm/°C |

| Drift with Supply Voltage  |                                          |      | 0.05   | 0.2        |       | 0.1      |      | %/Vott |

| Threshold Voltage          |                                          |      | 2/3    |            |       | 2/3      |      | x vcc  |

| Trigger Voltage            | V <sub>CC</sub> = 15V                    | 4.8  | 5      | 5.2        |       | 5        |      | V      |

|                            | VCC = 5V                                 | 1.45 | 1.67   | 1.9        |       | 1.67     |      | V      |

| Trigger Current            |                                          |      | 0.5    |            |       | 0.5      |      | μА     |

| Reset Voltage              |                                          | 0.4  | 0.7    | 1.0        | 0.4   | 0.7      | 1.0  | V      |

| Reset Current              |                                          |      | 0.1    |            |       | 0.1      |      | mA     |

| Threshold Current          | Note 3                                   |      | 0.1    | .25        |       | 0.1      | .25  | μА     |

| Control Voltage Level      | V <sub>CC</sub> = 15V                    | 9.6  | 10     | 10.4       | 9.0   | 10       | 11   | V      |

|                            | VCC = 5V                                 | 2.9  | 3.33   | 3.8        | 2.6   | 3.33     | 4    | v      |

| Output Voltage Drop (low)  | V <sub>CC</sub> = 15V                    |      |        |            |       | - Sec. 1 | 1000 | 568    |

|                            | ISINK = 10mA                             |      | 0.1    | 0.15       |       | 0.1      | .25  | v      |

|                            | ISINK = 50mA                             |      | 0.4    | 0.5        |       | 0.4      | .75  | V      |

|                            | ISINK " 100mA                            |      | 2.0    | 2.2        |       | 2.0      | 2.5  | v      |

|                            | ISINK = 200mA                            |      | 2.5    |            | 1     | 2.5      |      |        |

|                            | V <sub>CC</sub> = 5V                     | 1    |        | Laurence I |       |          |      | 2000   |

|                            | ISINK = 8mA                              | 10 5 | 0.1    | 0.25       |       |          |      | v      |

|                            | ISINK = 5mA                              |      |        |            |       | .25      | .35  |        |

| Output Voltage Drop (high) |                                          |      | V.     |            |       |          |      |        |

|                            | SOURCE = 200mA                           |      | 12.5   |            |       | 12.5     |      |        |

|                            | V <sub>CC</sub> = 15V                    |      |        |            |       |          |      |        |

|                            | SOURCE - 100mA                           |      |        |            |       |          |      |        |

|                            | V <sub>CC</sub> = 15V                    | 13.0 | 13.3   |            | 12.75 | 13.3     |      | V      |

|                            | VCC - 5V                                 | 3.0  | 3.3    |            | 2.75  | 3.3      |      | V      |

| Rise Time of Output        |                                          |      | 100    |            |       | 100      |      | nsec   |

| Fall Time of Output        | 1                                        |      | 100    |            |       | 100      |      | nsec   |

#### NOTES

- 1. Supply Current when output high typically 1mA less.

- 2. Tested at VCC = 5V and VCC = 15V

- 3. This will determine the maximum value of RA+ RB For 15V operation, the max total R = 20 megohm.

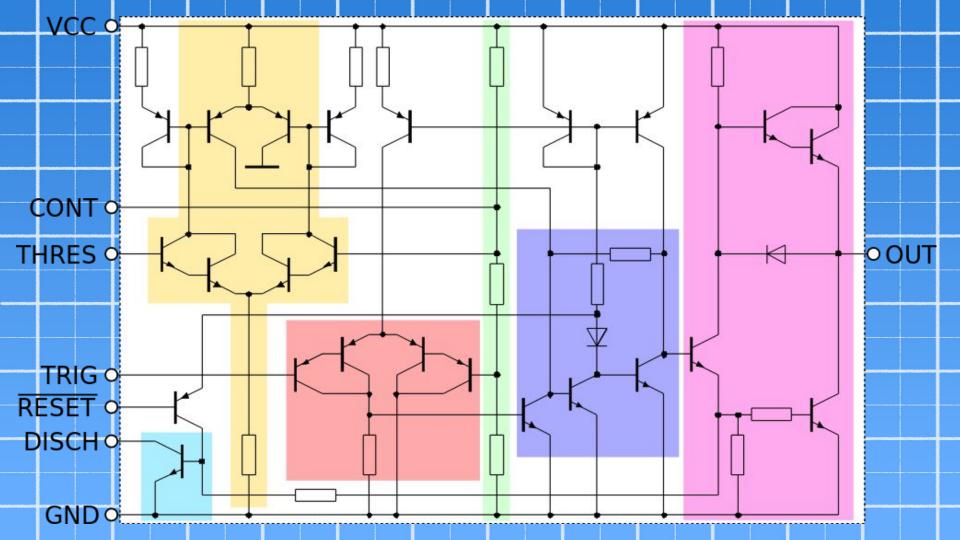

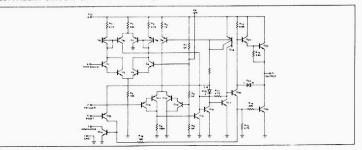

#### EQUIVALENT CIRCUIT (Shown for One Side Only)

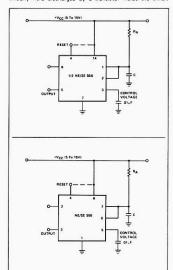

In this mode of operation, the timer functions as a oneshot. Referring to Figure 1a the external capacitor is initially held discharged by a transistor inside the timer.

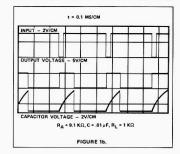

Upon application of a negative trigger pulse to pin 2, the flip-flop is set which releases the short circuit across the external capacitor and drives the output high. The voltage across the capacitor, now, increases exponentially with the time constant  $\tau = R_{AC}$ . When the voltage across the capacitor equals  $2.0 \ N_{CC}$ , the comparator resets the flip-flop which in turn discharges the capacitor rapidly and drives the output to its low state. Figure 1b shows the actual waveforms generated in this mode of operation.

FIGURE 1a.

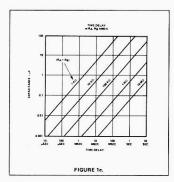

The circuit triggers on a negative going input signal when the level reaches 1/3 VCC. Once triggered, the circuit will remain in this state until the set time is elapsed, even if it is triggered again during this interval. The time that the output is in the high state is given by t=1. If  $\mu$ C and can easily be determined by Figure 1c. Notice that since the charge rate, and the threshold level of the comparator are both directly proportional to supply voltage, the timing

interval is independent of supply. Applying a negative pulse simultaneously to the reset terminal (pin 4) and the trigger terminal (pin 2) during the timing cycle discharges the external capacitor and causes the cycle to start over again. The timing cycle will now commence on the positive degle of the reset pulse. During the time the reset pulse is applied, the output is driven to its flow state.

When the reset function is not in use, it is recommended that it be connected to VCC to avoid any possibility of false triggering.

#### ASTABLE OPERATION

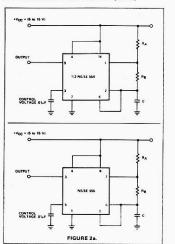

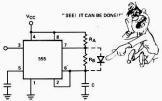

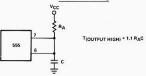

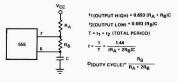

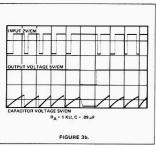

If the circuit is connected as shown in Figure 2a (pins 2 and 6 connected) it will trigger itself and free run as a multivibrator. The external capacitor charges through RA and RB and discharges through RB only. Thus the duty cycle may be precisely set by the ratio of these two resistors.

#### SIGNETICS TIMERS = 555/556

#### APPLICATIONS INFORMATION (Cont'd)

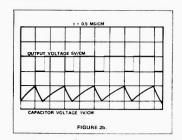

In this mode of operation, the capacitor charges and discharges between 1/3 VCC and 2/3 VCC. As in the triggered mode, the charge and discharge times, and therefore the frequency are independent of the supply voitage.

Figure 2b shows actual waveforms generated in this mode of operation.

The charge time (output high) is given by:

Thus the total period is given by:

The frequency of oscillation is then:

$$f = \frac{1}{T} = \frac{1.44}{(R_A + 2R_B) C}$$

and may be easily found by Figure 2c.

The duty cycle is given by:

$$= \frac{R_B}{R_A + 2R_B}$$

THE DEVICE TRIGGERS ON THE NEGATIVE GOING EDGE OF A LOW GOING PULSE. THE TRIGGER PULSE MUST BE OF SHORTER DURATION THAN THE "RC" TIME INTERVAL. IF THE TRIGGER IS NELD LOW, THE OUTPUT WILL STAY HIGH UNTIL TRIGGER IS DRIVEN HIGH AGAIN.

#### MAXIMUM OSCILLATION FREQUENCY

THE 555 TIMER IS CAPABLE OF OSCILLATING AT UP TO 300 KHz. HOWEVER, FOR TEMPERATURE STAB-ILITY THE LIMIT SHOULD BE AROUND 200 KHz.

11

# GUARANTEED NOT TO RESET VCC GUARANTEED NOT TO RESET VCC GUARANTEED RESET

THE RESET ACTS AS AN INHIBIT. WHEN THE RESET (PIN 4) IS ABOVE 1 VOLT THE DEVICE IS FREE TO FUNCTION. IF THE RESET IS TAKEN BELOW. 4 VOLTS, THE OUTPUT IS FORCED LOW. WHEN THE RESET IS RELEASED, THE OUTPUT WILL STILL REMAIN LOW UNTIL A TRIGGER PULSE IS APPLIED.

THE IMITIAL ACCURACY IS THE TIMING REPEATABILITY FROM DEVICE TO DEVICE AND ALSO THE SAME DEVICE TODAY, TO MORROW AND 3 YEARS FROM NOW, WITH THE SAME "RC" NETWORK AND SUPPLY VOLTAGE. TYPICALLY, THE NE55S HAS A 1% INITIAL ACCURACY.

#### THRESHOLD VOLTAGE

WHEN TRIGGERED, THE TIMER STARTS ITS TIMING CYCLE BY DRIVING THE OUTPUT, PIN 3, HIGH, SIMULTANEOUSLY, THE TIMING CAPACITOR STARTS CHARGING FROM ITS STADY STATE LEVEL AT GROUND. WHEN IT REACHES 2/3  $V_{\rm CC}$ , AN INTERNAL COMPARATOR IS TRIPPED, CAUSING THE CAPACITOR TO DISCHARGE TO GROUND. THIS DRIVES THE OUTPUT LOW, ENDING THE MIMING CYCLE.

#### TRIGGER VOLTAGE

THE TRIGGER PULSE MUST DROP BELOW 1/3 OF THE SUPPLY VOLTAGE BEFORE THE TIMER TRIGGERS.

13

THE TIMING OF THE DEVICE WILL VARY SLIGHTLY WITH CHANGE IN SUPPLY VOLTAGE. THE TYPICAL TIMING DRIFT IS 0.1% PER VOLT.

#### TIMING DRIFT W/ TEMPERATURE

THE TIMER IN THE MONCSTABLE MODE HAS A TIMING DRIFT OF 50 PPM/°C TYPICAL. IN THE ASTABLE MODE, SINCE BOTH COMPARATIONS OF THE DEVICE ARE USED, THE DRIFT IS SOMEWHAT GREATER. TYPICALLY 150 PPM/°C DRIFT.

#### DUTY CYCLE

THE DUTY CYCLE IS "ON TIME" EXPRESS IN TERMS OF TOTAL CYCLE TIME. THE DUTY CYCLE IS LIMITED, UNDER NORMAL CIRCUMSTANCES, TO 50%. HOWEVER, BY ADDING A DIODE A DUTY CYCLE OF LESS THAN 50% CAN BE ACHIEVED.

#### LATCH UP WHEN DRIVING AN INDUCTIVE LOAD

A NEGATIVE VOLTAGE AT PIN 3 CAN CAUSE A LATCH UP. THE SOLUTION IS TO ADD TWO DIODES AS SHOWN. THIS CIRCUIT PROHIBITS A NEGATIVE VOLTAGE FROM REACHING PIN 3.

PIN 5, THE CONTROL VOLTAGE PIN, IS PRIMARILY USED FOR FLITERING MEN DEVICE IS USED IN NOISY EVENIGNOS, HOVEVER, BY IMPOSING A VOLTAGE AT THIS POINT, IT IS POSSIBLE TO VARY THE TIMING OF THE EVICLE INDEPENDENTLY OF THE "AR" NETWORK. THE CONTROL VOLTAGE MAY BE VARIED FROM 45% TO 95% OF V<sub>CC</sub> IN THE MONDSTABLE MODE, AND FROM 17, VOLTS TO V<sub>CC</sub>. IN THE ASTABLE MODE.

#### FORMULA

#### MONOSTABLE TIMING

#### ASTABLE TIMING

THE RESERVE THE PERSON NAMED IN COLUMN

15

#### SIGNETICS TIMERS = 555/556

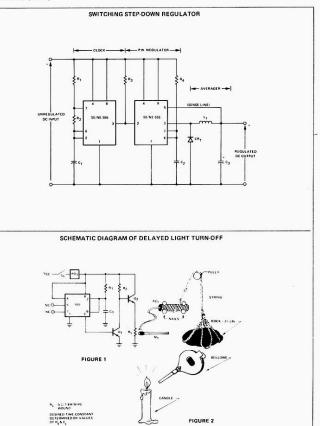

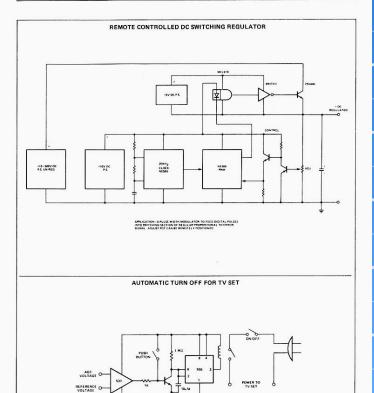

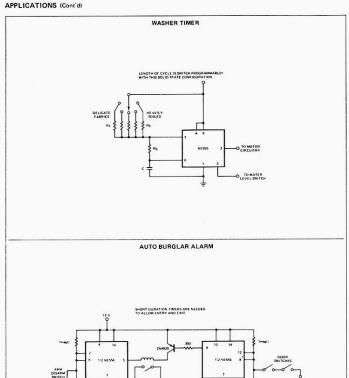

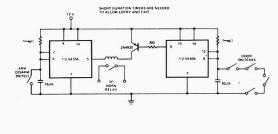

### HERE ARE SOME ADDITIONAL INGENIOUS APPLICATIONS DEVISED BY SIGNETICS ENGINEERS AND SOME OF OUR CUSTOMERS.

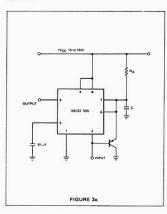

#### MISSING PULSE DETECTOR

Using the circuit of Figure 3a, the timing cycle is continuously reset by the input pulse train. A change in frequency, or a missing pulse, allows completion of the timing cycle which causes a change in the output level. For this application, the time delay should be set to be slightly longer than the normal time between pulses. Figure 3b shows the actual waveforms seen in this mode of operation.

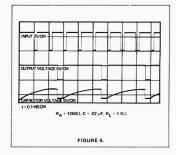

#### FREQUENCY DIVIDER

If the input frequency is known, the timer can easily be used as a frequency divider by adjusting the length of the timing cycle. Figure 4 shows the waveforms of the timer in Figure 1a when used as a divide by three circuit. This application makes use of the fact that this circuit cannot be retrigered during the timing cycle.

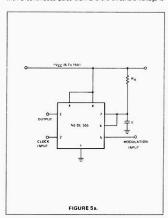

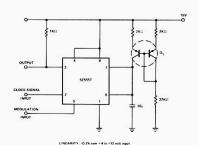

#### PULSE WIDTH MODULATION (PWM)

In this application, the timer is connected in the monostable mode as shown in Figure 5a. The circuit is triggered with a continuous pulse train and the threshold voltage is

#### SIGNETICS TIMERS = 555/556

#### APPLICATIONS INFORMATION (Cont'd)

modulated by the signal applied to the control voltage terminal (pin 5). This has the effect of modulating the pulse width as the control voltage varies. Figure 5h shows the actual waveforms generated with this circuit.

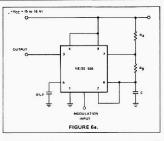

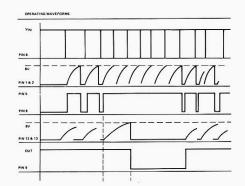

#### PULSE POSITION MODULATION (PPM)

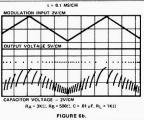

This application uses the timer connected for satable (freerunning) operation. Figure 6a, with a modulating signal again applied to the control voltage terminal. Now the pulse position varies with the modulating signal, since the threehold voltage and hence the time delay is varied. Figure 6b shows the waveforms generated for triangle wave modulation signal.

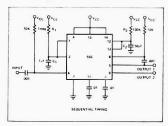

#### TEST SEQUENCER

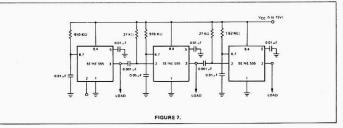

Figure 7 shows several timers connected sequentially. The first timer is started by momentarily connecting pin 2 to ground, and runs for 10 msec. At the end of its timing cycle, it triggers the second circuit which runs for 50 msec. After this time, the third circuit is triggered. Note that the timing resistors and capacitors can be programmed digitally and that each circuit could easily trigger several other timers to start concurrent sequences.

18

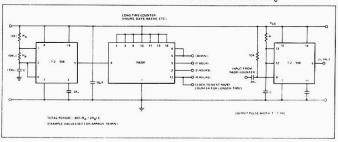

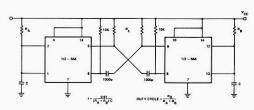

#### LONG TIME DELAYS

In the 556 timer the timing is a function of the charging rate of the external capacitor. For long time delays expensive capacitors with extremely low leakage are required. The practicality of the components involved limits the time between pulses to something in the neighborhood of ten minutes.

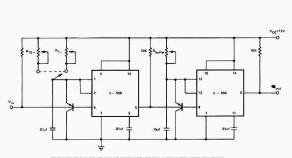

To achieve longer time periods both halves may be connected in tandem with a "Divide-by" network in between the first timer section operates in an oscillatory mode with a period of 14 $^{\circ}$ C.

This signal is then applied to a "Divide-by-N" network to give an output with the period of  $N/\ell_0$ . This can then be used to trigger the second half of the 556. The total time delay is now a function of N and  $\ell_0$ .

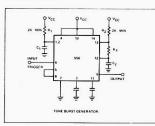

#### TONE BURST GENERATOR

The 556 Dual Timer makes an excellent Tone Burst Generator. The first half is connected as a one shot and the second half as an oscillator.

The pulse established by the one shot turns on the oscillator allowing a burst of pulses to be generated.

#### SEQUENTIAL TIMING

One feature of the Dual Timer is that by utilizing both halves it is possible to obtain sequential timing. By con-

necting the output of the first half to the input of the second half via a .001 $\mu$ fd coupling capacitor sequential timing may be obtained. Delay  $t_1$  is determined by the first half and  $t_2$  by the second half delay.

The first half of the timer is started by momentarily connecting pin 6 to ground. When it is timed out (determined by 1.18,10) the second half begins. Its time duration is determined by 1.18,202).

#### SIGNETICS TIMERS = 555/556

#### APPLICATIONS

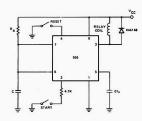

#### SIMPLE TIME DELAY

#### SIMPLE TIME DELAY

20

#### DUAL ASTABLE

THIS CIRCUIT MAINTAINS THE TEMPERATURE STABILITY OF THE MONOSTABLE MODE FOR ASTABLE OPERATION. IT ALSO ALLOWS A LOAD TO BE DRIVEN IN PUSH-PULL.

#### TOUCH CONTROL

THE 27K RESISTOR IS SUITABLE FOR INDUSTRIAL OR PUBLIC ENVIRONMENTS. WITH LOWER AMBIENT NOISE, A HIGHER VALUE OF RESISTOR MAY BE NECESSARY.

APPLICATIONS (Cont'd)

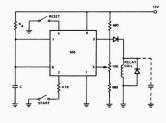

#### BURGLAR ALARM

INTERRUPTION OF INCIDENT LIGHT TO THE PHOTOTRANSISTOR CAUSES CURRENT TO FLOW THROUGH THE LOAD.

#### TTL MONOSTABLE

THIS CIRCUIT HAS SUPERIOR TIMING ACCURACY TO CONVENTIONAL TTL MONOSTABLES. THE 4.7/K RESISTOP MAY BE REPLACED BY A DIODE, HAVING THE CATHODE TO THE GATE.

23

#### APPLICATIONS (Cont'd)

#### PHOTOGRAPHIC TIMER

THE SMALL INDUCTOR IN THE LOAD IS TO REDUCE VOLTAGE SPIKES AT SWITCH-ON. IT MAY BE OMITTED IF MAINS SPIKES CAN BE TOLERATED. TO REDUCE RADIATED NOISE FURTHER, THE TRIAC MAY BE DRIVEN FROM A GATED ZERO-CROSSING SWITCH.

#### LINEAR PULSE WIDTH MODULATOR

THE 15V SUPPLY MUST BE WELL-REGULATED.

#### APPLICATIONS (Cont'd)

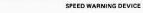

THE INPUT PULSE TRAIN IS DERIVED FROM A TRANSDUCER SENSING THE VEHICLE PROPELLOR SHAFT. THE OUTPUT OF THE SECOND TIMER GOES LOW WHEN A PRESET SPEED IS EXCEEDED.

#### OPERATING WAVEFORMS

:

#### SIGNETICS TIMERS = 555/556

#### APPLICATIONS (Cont'd)